www.afm-iournal.de

# Water-Induced Scandium Oxide Dielectric for Low-Operating Voltage n- and p-Type Metal-Oxide **Thin-Film Transistors**

Ao Liu, Guoxia Liu, Huihui Zhu, Huijun Song, Byoungchul Shin, Elvira Fortunato, Rodrigo Martins, and Fukai Shan\*

Solution-processed metal-oxide thin films based on high dielectric constant (k) materials have been extensively studied for use in low-cost and high-performance thin-film transistors (TFTs). Here, scandium oxide (ScO<sub>x</sub>) is fabricated as a TFT dielectric with excellent electrical properties using a novel water-inducement method. The thin films are annealed at various temperatures and characterized by using X-ray diffraction, atomic-force microscopy, X-ray photoelectron spectroscopy, optical spectroscopy, and a series of electrical measurements. The optimized ScOx thin film exhibits a low-leakage current density of 0.2 nA cm<sup>-2</sup> at 2 MV cm<sup>-1</sup>, a large areal capacitance of 460 nF cm<sup>-2</sup> at 20 Hz and a permittivity of 12.1. To verify the possible applications of ScO<sub>x</sub> thin films as the gate dielectric in complementary metal oxide semiconductor (CMOS) electronics, they were integrated in both n-type InZnO (IZO) and p-type CuO TFTs for testing. The water-induced full oxide IZO/ScO<sub>x</sub> TFTs exhibit an excellent performance, including a high electron mobility of 27.7 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, a large current ratio  $(I_{\rm on}/I_{\rm off})$  of 2.7  $\times$  10<sup>7</sup> and high stability. Moreover, as far as we know it is the first time that solution-processed p-type oxide TFTs based on a high-k dielectric are achieved. The as-fabricated p-type CuO/ScO, TFTs exhibit a large  $I_{\rm on}/I_{\rm off}$  of around 10<sup>5</sup> and a hole mobility of 0.8 cm<sup>2</sup> V<sup>-1</sup> at an operating voltage of 3 V. To the best of our knowledge, these electrical parameters are among the highest performances for solution-processed p-type TFTs, which represents a great step towards the achievement of low-cost, all-oxide, and low-power consumption CMOS logics.

A. Liu, Dr. G. X. Liu, H. H. Zhu, H. J. Song, Prof. F. Shan College of Physics and Lab of New Fiber Materials and Modern Textile Growing Base for State Key Laboratory Qingdao University Qingdao 266071, P. R. China E-mail: fkshan@qdu.edu.cn Dr. B. C. Shin **Electronic Ceramics Center** DongEui University Busan 614-714, Korea Dr. E. Fortunato, Dr. R. Martins Department of Materials Science/CENIMAT-I3N Faculty of Sciences and Technology New University of Lisbon and CEMOP-UNINOVA Campus de Caparica

DOI: 10.1002/adfm.201502612

2829-516 Caparica, Portugal

In the past decade amorphous metaloxide thin-film transistors (TFTs) have been studied in depth for applications in active-matrix organic light-emitting diodes (AMOLEDs), solar cells, biosensor arrays, and photodetectors.[1] Along with the rapid developments in display technology, highresolution and high-speed displays have become one of the growing trends. In this regard, energy consumption has turned out to be an inevitable issue especially for mobile, battery-powered applications. As a low-voltage operation of the oxide TFTs is demanded for practical applications, it is necessary to develop novel gate dielectrics for producing a large areal capacitance.<sup>[2]</sup> The achievements of low-voltage oxide TFTs have been extensively reported in recent works, including the use of inorganic high-k dielectrics,[3] organic self-assembled-monolayer dielectrics, [4] and electrolyte dielectrics.<sup>[5]</sup> Among these, the use of inorganic high-k dielectrics is the most attractive option as it simultaneously enables a low leakage current, through the use of a thicker film, as well as a low-voltage operation. The high-*k* dielectrics can be prepared by various methods such as metal anodic oxi-

dation method, [6] vacuum-based deposition, [7] and low-cost solution-based techniques.<sup>[8]</sup> To date, there are numerous candidate materials (e.g., Ta<sub>2</sub>O<sub>5</sub>,<sup>[7b]</sup> Y<sub>2</sub>O<sub>3</sub>,<sup>[7a,9]</sup> Al<sub>2</sub>O<sub>3</sub>,<sup>[10]</sup> ZrO<sub>2</sub>,<sup>[2,11]</sup> HfO<sub>2</sub>,<sup>[8a]</sup> LaAlO<sub>3</sub>, [8b] HfON, [12] silicates, [13] etc.) that could potentially replace conventional dielectrics, such as SiO2 and SiNx. To the best of our knowledge, there are few reports on the demonstration of scandium oxide (Sc<sub>2</sub>O<sub>3</sub>) as the gate dielectric in TFT devices.

As a high-k material Sc<sub>2</sub>O<sub>3</sub> has a dielectric constant of 14, a bandgap of 6.3 eV and an excellent thermal stability with Si.[14] In addition, Sc<sub>2</sub>O<sub>3</sub> has been found to possess a negative fixed charge. This is beneficial to obtain a positive threshold or turnon voltage for n-type TFTs that operate in the enhancement mode.[15]

Concerning the CMOS architecture development based on solution processing, a wet step is inevitably involved. In this regard, the resistance to moisture absorption is another important

ADVANCED FUNCTIONAL MATERIALS

www.afm-journal.de

issue for the selection of the high-k dielectric material. [16] La<sub>2</sub>O<sub>3</sub> has been previously regarded as a promising dielectric material because of its large band offset of 2.3 eV and high dielectric constant of 30.[3b] Unfortunately, the high moisture absorption of La<sub>2</sub>O<sub>3</sub> limits its practical application in CMOS processes. Zhao et al. have proved that the moisture absorption in high-k oxides transforms metal oxides (M<sub>m</sub>O<sub>n</sub>) into metal hydroxides  $(M(OH)_n)$ . [17] The moisture absorption speed is strongly related to the change in Gibbs free energy,  $\Delta G$ , during the reaction. Here, a negative  $\Delta G$  means a decrease in the system energy after the reaction, indicating the occurrence of transformation reactions. According to the  $\Delta G$  calculation, only two high-k materials ( $Sc_2O_3$  and  $HfO_2$ ) showed positive  $\Delta G$  values, indicating a high resistance to moisture absorption, and thus not the occurrence of a transformation reaction. It is well known that the first and commonly used high-k gate dielectric in commercial production is a Hf-based oxide material.[8a] As an alternative to that we propose Sc<sub>2</sub>O<sub>2</sub> as an excellent dielectric candidate for further development of high-performance, low processing costs, and low power consumption CMOS logics.<sup>[18]</sup>

To date, Sc<sub>2</sub>O<sub>3</sub> thin films have been prepared by using various costly vacuum-based techniques, such as molecular-beam epitaxy, [14b] chemical vapor deposition, [14a,19] electron-beam evaporation,<sup>[20]</sup> and high-pressure sputtering.<sup>[14c]</sup> In contrast. solution processing usually exhibits benefits such as simplicity, atmospheric processing, high throughput, large-area uniformity, roll-to-roll capability, and low fabrication cost.[21] However, solution-processed metal oxide thin films are usually fabricated from metal-organic precursors that contain large amounts of organic species. The thermal decomposition of these organic species tend to lead to disruptive volume changes, rough surfaces, and highly porous films. [22] In our recent report a waterinducement method was used for the first time to fabricate metal-oxide thin films and integrate these as channel layer in TFT devices.<sup>[23]</sup> This water-inducement route allows the preparation of precursor solutes in water without additional additives and catalysts. Therefore, the decomposition and densification of the oxide films can be achieved at lower annealing temperatures  $(T_a)$  compared to that of commonly used organic-based precursors. Moreover, the surface morphology of the annealed films is smoother due to the release and decomposition of small nitrate groups. Apart from that, the water-inducement method is simple and non-toxic and so has all the expected characteristics to substitute the commonly used organic-based synthetic approaches to fabricate full metal oxide based devices for the next generation of low cost and functional electronics.

In previous reports on solution-processed TFTs the channel layers were mostly composed of n-type metal oxides, which prevent the implementation of the complementary logic-based circuits with oxide TFTs. This is mainly related to the lack of p-type oxide semiconductors and the difficulty in growing high-quality film via a low-temperature process. [24] Recently, several groups have carried out research on exploring solution-processed p-type oxide TFTs. Kim et al. [25] demonstrated a spin-coated Cu<sub>2</sub>O TFT at 700 °C with a field-effect mobility ( $\mu_{\rm FE}$ ) of 0.16 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and an on/off current ratio ( $I_{\rm on}/I_{\rm off}$ ) of 10<sup>2</sup>. Anthopoulos's group[26] produced Cu<sub>2</sub>O thin films by spray pyrolysis at a maximum temperature of 275 °C for 12 h and the as-fabricated Cu<sub>2</sub>O TFTs exhibited an average  $\mu_{\rm FE}$  of

$3\times10^{-4}~\rm cm^2~V^{-1}~s^{-1}$ . Solution-processed p-type SnO TFTs were achieved by Okamura and co-workers,  $^{[27]}$  exhibiting a  $\mu_{\rm FE}$  of the order of 0.13 cm $^2$  V $^{-1}$  s $^{-1}$  and an  $I_{\rm on}/I_{\rm off}$  of 85. Garlapati et al.  $^{[28]}$  fabricated a low-operating voltage CuO TFT based on a polymer electrolyte dielectric at 400 °C. The CuO TFT exhibited a  $\mu_{\rm FE}$  of 0.22 cm $^2$  V $^{-1}$  s $^{-1}$  and an  $I_{\rm on}/I_{\rm off}$  of 10 $^3$  at a low operating voltage of 1.5 V. As can be seen, the production of p-type oxide TFTs via low-temperature solution processing is highly demanded for the development of next-generation, low-cost, all-oxide based CMOS logics.

To accomplish this demand, herein we report for the first time a solution processed, p-type, metal-oxide TFT that uses a dielectric high-k ScO $_x$  thin film fabricated by a simple water-inducement route. The physical properties of the ScO $_x$  thin films as a function of annealing condition were systematically investigated. To verify the potential of ScO $_x$  thin films as the gate dielectric in CMOS logics, their applications in n-type and p-type metal oxide TFTs were evaluated. In particular, we noticed that the p-type CuO/ScO $_x$  TFT exhibited a high performance under a low operating voltage of 3 V, with a high  $I_{\rm on}/I_{\rm off}$  of around  $10^5$ , and a hole mobility of ca. 0.8 cm $^2$  V $^{-1}$  s $^{-1}$ .

## 2. Results and Discussion

#### 2.1. Characterization of Water-Induced (WI) ScO<sub>x</sub> Precursor

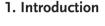

The thermal behavior of the WI  $ScO_x$  xerogel was investigated by thermogravimetic analysis (TGA) and the results are shown in **Figure 1**. The weight loss starting at around 100 °C is due to the evaporation of water, which was used as the solvent in the WI precursor solution. The molecules were drawn together during the evaporation of the solvent, which led to the transition from the 'sol' to the 'gel' state. [29] The subsequent weight loss can be attributed to the thermal decomposition of metal nitrate and the evaporation of the volatile nitrate precursor. [30] The dehydroxylation of the scandium hydroxide precursor occurred at around 260 °C and was completed at around 450 °C. No apparent weight loss was observed at temperatures above 450 °C, implying a complete conversion from the xerogel into scandium oxide.

Figure 1. Thermal behavior of the WI  $ScO_x$  xerogel.

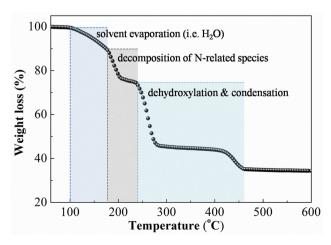

Figure 2. Optical transmittances of ScO<sub>x</sub> dielectric thin films annealed at different temperatures. The inset shows the Tauc plots of the corresponding ScO<sub>x</sub> thin films.

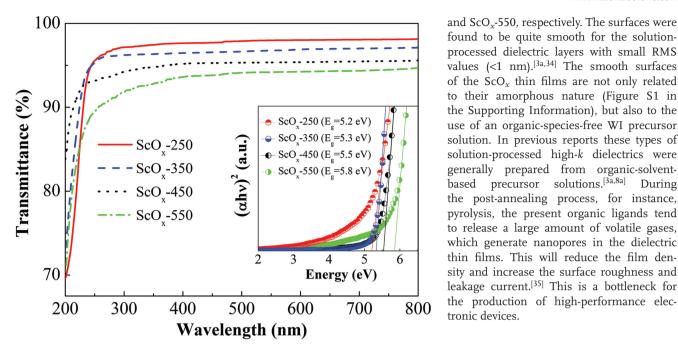

## found to be quite smooth for the solutionprocessed dielectric layers with small RMS values (<1 nm).[3a,34] The smooth surfaces of the ScOx thin films are not only related to their amorphous nature (Figure S1 in the Supporting Information), but also to the use of an organic-species-free WI precursor solution. In previous reports these types of solution-processed high-k dielectrics were generally prepared from organic-solventbased precursor solutions.[3a,8a] During the post-annealing process, for instance, pyrolysis, the present organic ligands tend to release a large amount of volatile gases, which generate nanopores in the dielectric thin films. This will reduce the film density and increase the surface roughness and leakage current.[35] This is a bottleneck for the production of high-performance electronic devices.

## 2.2. Optical Properties of WI ScOx Thin Films

The novel fabricated WI ScO<sub>x</sub> thin films were characterized by UV-vis transmittance measurements. All thin films exhibited average transmittances of over 94% in the visible range. Moreover, we noticed that the transmittance of the  $ScO_x$  thin films decreased as  $T_a$  increased. This decrease can be attributed to the slight increase in surface roughness or the elimination of interstitial oxygen at high annealing temperatures.<sup>[31]</sup> The optical bandgap ( $E_{\alpha}$ ) was calculated using a standard Tauc plot method<sup>[32]</sup> and the results are shown in the inset of Figure 2. The  $E_g$  value increased from 5.2 to 5.8 eV as  $T_a$  was enhanced from 250 to 550 °C. Larger  $E_{\rm g}$  values make it possible to inhibit the carrier conduction between the channel layer and the dielectric layer. For the low-temperature-processed ScO<sub>x</sub> thin film, the presence of defects in the thin film would produce localized states in the bandgap, which decreases the bandgap energy of the thin film. At high  $T_a$ , the annihilation of oxygen vacancies/ defects results in a decrease of the density of states in the band structure, which leads to an increase of the bandgap energy of the  $ScO_x$  thin films.<sup>[33]</sup>

## 2.3. Surface Morphologies and Structural Properties of WI ScO<sub>x</sub> Thin Films

It is well known that for high-performance TFTs it is critical to have a dielectric layer with a smooth surface as the carrier transport is highly influenced by the interface between the channel and the dielectric layers. The atomic force microscopy (AFM) images of the  $ScO_x$  thin films as a function of  $T_a$  are shown in Figure 3. The root mean square (RMS) values were 0.17, 0.17, 0.23, and 0.57 nm for  $ScO_x$ -250,  $ScO_x$ -350,  $ScO_x$ -450,

## 2.4. Analysis of XPS Results for WI ScO, Thin

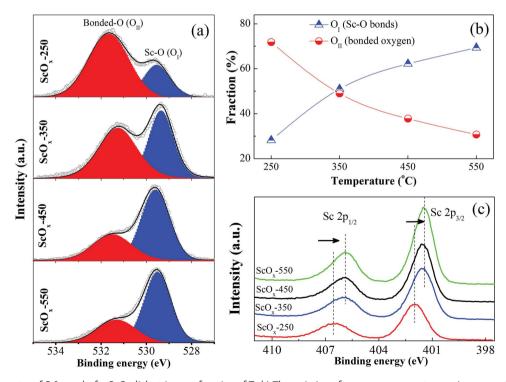

The chemical compositions of WI  $ScO_x$  thin films were explored by XPS measurements. The O 1s binding energies of the ScO<sub>x</sub> thin films fabricated at various temperatures are shown in Figure 4a. The binding energies of the O 1s peaks were deconvoluted into two peaks centered at 531.6 eV and 529.6 eV. The peaks centered at 529.6 eV and 531.6 eV can be assigned to the  $O^{2-}$  in  $ScO_x$  and the bonded oxygen, respectively, whereby the latter could be an oxygen vacancy, hydroxyl group, or absorbed H<sub>2</sub>O on the film surface . For convenience, O<sub>I</sub>/O<sub>total</sub> and O<sub>II</sub>/O<sub>total</sub> are defined as the relative quantity of O<sup>2-</sup> in  $ScO_x$  and the bonded oxygen in the  $ScO_x$  thin films, respectively. The ratios of  $O_{\text{I}}/O_{\text{total}}$  and  $O_{\text{II}}/O_{\text{total}}$  are summarized in Figure 4b. We found that with increasing  $T_a$  from 250 °C to 550 °C, the fraction of O<sup>2-</sup> in ScO<sub>x</sub> increases from 28.2% to 69.3%. The XPS results reveal that the bonded oxygen ions are removed and M-O bonds are created during the oxidation of the ScO<sub>x</sub> thin films. Therefore, to be used as a good dielectric layer, the amount of bonded oxygen in the film should be kept at a relatively low level because the bonded oxygen generally creates defect states in the forbidden band of ScO<sub>x</sub>, which will induce a leakage current and will lower the breakdown electric field.

Figure 4c exhibits the XPS Sc 2p spectra of ScO<sub>x</sub> dielectrics annealed at various temperatures. All samples show the typical Sc 2p spectra with spin-orbit doublets ( $p_{3/2}$  and  $p_{1/2}$ ) separated by 4.4 eV, which indicates the formation of  $ScO_x$ . The atomic ratios (Sc/O) for ScO<sub>x</sub>-250, ScO<sub>x</sub>-350, ScO<sub>x</sub>-450, and ScO<sub>x</sub>-550 were calculated to be 1:3, 1:2.2, 1:2, and 1:1.9, respectively. As  $T_a$ was increased, both Sc 2p peaks shifted to lower binding energies. A similar phenomenon was reported previously[10a,36] for solution-processed ZrO<sub>x</sub> and AlO<sub>x</sub> films. The reasons for this shift can mainly be attributed to the progressive oxidization of ScO<sub>x</sub> or to the decrease in the coordination number of M<sup>n+</sup> ions in the film.

Figure 3. Surface morphologies of a)  $ScO_x$ -250, b)  $ScO_x$ -350, c)  $ScO_x$ -450, and d)  $ScO_x$ -550.

Figure 4. a) XPS spectra of O 1s peaks for  $SCO_x$  dielectrics as a function of  $T_a$ . b) The variation of oxygen components at various annealing temperatures. c) The corresponding XPS Sc 2p spectra of the ScO<sub>x</sub> thin films.

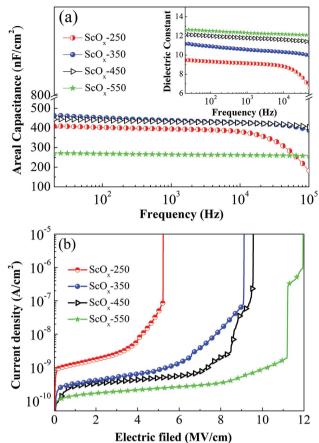

**Figure 5.** Variation of a) the *C-f* and b)  $J_{\text{leak}}$ –E characteristics for Al/ScO $_{x}$ /p<sup>+</sup>-Si capacitors.

#### 2.5. Dielectric and Electrical Properties of WI ScO, Dielectric

To investigate the dielectric and electrical properties of the WI ScO<sub>x</sub> thin films annealed at various temperatures, capacitors with a structure of  $Al/ScO_x/p^+-Si$  were used. Figure 5a shows the areal capacitance (C) as a function of frequency (f) for  $ScO_x$ capacitors. The corresponding dielectric constant dispersions are shown in the inset of Figure 5a. The capacitance densities at 20 Hz were found to be 408, 460, 450, and 270 nF cm<sup>-2</sup> for ScO<sub>x</sub>-250, ScO<sub>x</sub>-350, ScO<sub>x</sub>-450, and ScO<sub>x</sub>-550, respectively. In the low-frequency region the areal capacitance increased as  $T_a$  increased from 250 to 350 °C and then decreased again for thin films annealed at temperatures higher than 350 °C. The reason for the increase of the capacitance for ScO<sub>x</sub>-350 °C can be attributed to the thermally enhanced dehydroxylation once the capacitance of the metal hydroxide is smaller than that of the metal oxide. [9] When the  $T_a$  was higher than 350 °C most of the scandium hydroxide was converted into ScO<sub>x</sub>. The decrease in the capacitance can be mainly attributed to the existence of a metal-silicate interface.[37] Assuming that the interfacial layer between Si and ScOx is mostly comprised of SiO<sub>2</sub>, the measured ScO<sub>x</sub> capacitance corresponds

to the combination of capacitors in series:

$$\frac{1}{G_{total}} = \frac{1}{G_{total}} + \frac{1}{G_{total}}$$

By introducing the k values and the thickness of the films, the decreased capacitance at higher annealing temperatures (>350 °C) can be well explained by the dominant role played by the SiO<sub>2</sub>-like capacitor (details not shown here).

Figure 5b shows the leakage current density ( $J_{\rm leak}$ ) versus electric field (E) measurements carried out to evaluate the leakage behavior of the  $ScO_x$  thin films. The relatively large  $J_{\rm leak}$  for  $ScO_x$ -250 is mainly related to the defects associated with the residual nitrate and hydroxyl groups. The leakage current profiles were found to decrease in slope as  $T_a$  increased indicating a reduction in the electronic defects as the annealing temperature increased. The current density levels for  $ScO_x$ -350 and  $ScO_x$ -450 were similar (less than 0.3 nA cm<sup>-2</sup> at 2 MV cm<sup>-1</sup>). Although the  $ScO_x$ -550 dielectric film had the lowest  $J_{\rm leak}$  value, it also showed the smallest areal capacitance, which would undoubtedly limit its performance in electronic devices.

#### 2.6. Solution-Processed n-Type IZO/ScO<sub>x</sub> TFTs

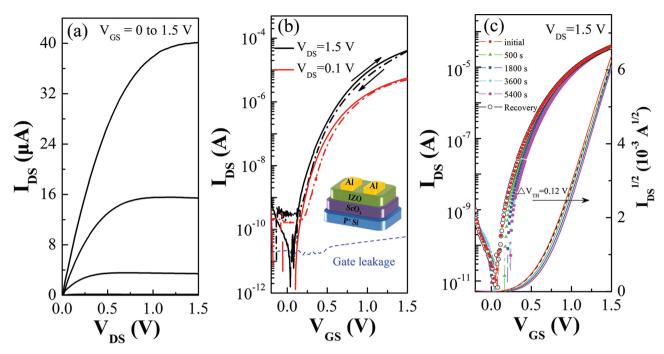

To verify the possible application of ScO<sub>x</sub> thin films as gate dielectrics, bottom-gated TFTs combined with a WI n-type IZO channel and p-type CuO channel were separately evaluated. In this study ScO<sub>x</sub>-350 was selected as the best dielectric layer because of its relatively low J<sub>leak</sub> and large capacitance. Moreover, temperatures lower than 350 °C are generally needed to employ a solution process in practical fabrication processes for flat-panel displays. [38] For the WI n-type IZO/ScO<sub>x</sub> TFT, the typical output and transfer curves are shown in Figure 6a,b. The IZO/ScO<sub>x</sub> TFT shows a high electrical performance, such as a high  $\mu_{\rm FE}$  of 27.7 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, an  $I_{\rm on}/I_{\rm off}$  of around 10<sup>7</sup>, a small SS value of 100 mV dec<sup>-1</sup>, a turn-on voltage  $(V_{on})$  close to 0 V, and a hysteresis of about 0.06 V. Here, we would like to emphasize that these as-fabricated TFTs can be operated at an ultra-low voltage of 1.5 V, which is 20 times lower than that for conventional SiO<sub>2</sub>-based TFTs (Figure S2, Supporting Information). This is because of the high k value and the small thickness of the ScO<sub>x</sub> dielectric. The negligible hysteresis observed indicates that there are small amounts of bulk traps within the IZO channel layer and interface traps between the ScO<sub>x</sub> dielectric and the IZO channel layer. The maximum areal density of states  $(N_s^{\text{max}})$  calculated from the SS value (see Experimental Section) was  $3 \times 10^{12}$  cm<sup>-2</sup> for the IZO/ScO<sub>x</sub> TFT. Such an  $N_s^{\text{max}}$  value is quite acceptable compared to previously reported TFTs based on solution-processed high-k dielectrics, such as  $YO_x$  (2.7 × 10<sup>12</sup> cm<sup>-2</sup>), [9]  $AlO_x$  (1.1 × 10<sup>12</sup> cm<sup>-2</sup>),  $ZrO_x$  $(7.6 \times 10^{12} \text{ cm}^{-2})$ , [3a] and HfO<sub>x</sub>/AlO<sub>x</sub> (1.6 × 10<sup>12</sup> cm<sup>-2</sup>). [39] Thus, the small  $N_s^{\text{max}}$  obtained indicates that the  $ScO_x$  thin films are highly attractive as dielectric to produce TFTs with excellent electrical performances, once the channel/dielectric interface is highly improved, from which the carrier transport in the interface region benefits as well as the overall device operational stability.

www.afm-journal.de

Figure 6. a) Output and b) transfer characteristics of the IZO/ScO<sub>x</sub> TFT. c) Transfer characteristics of the IZO/ScO<sub>x</sub> TFT with a  $V_G$  of 1.5 V for 5400 s and its recovery behavior.

Although oxide TFTs based on a high-k dielectric obtained via a low-temperature solution process have been previously realized, to the best of our knowledge there has been no reports to demonstrate their electrical stability under long-term bias stressing. To investigate the bias stability of the WI IZO/ScO<sub>x</sub> TFT positive bias stress (PBS) tests were performed by applying a constant gate bias of 1.5 V whereby the source and drain electrodes were grounded. The device was stressed for 5400 s and allowed to recover in the dark. The results are shown in Figure 6c. The TFT exhibited an acceptable operational stability with a small threshold voltage shift ( $\Delta V_{TH}$ ) of 0.12 V, which returned to its original position after 120 min. The negligible change in the SS value reveals that there is no additional defect creation at the channel/dielectric interface during bias stressing. The small  $\Delta V_{TH}$  shift value reveals that there are a small number of defects at the IZO/ScO<sub>x</sub> interface, which is consistent with the  $N_s^{\text{max}}$  data.

In this work, an areal capacitance of 460 nF cm<sup>-2</sup> was obtained at a frequency of 20 Hz to avoid mobility overestimation. [40] It should be noted that by replacing SiO<sub>2</sub> with the high-k ScO<sub>x</sub> dielectric, the  $\mu_{\rm FE}$  was significantly enhanced by a factor of 9. This increase in  $\mu_{\rm FE}$  benefits from both the electronically clean interface and the high capacitance density of the ScO<sub>x</sub> dielectric. In the oxide semiconductors, the carrier transport is governed by dense localized states within the forbidden

**Figure 7.** a) Schematic of electron-transporting mode and b) energy-band diagram in n-type amorphous oxide semiconductors.

bandgap, although the overlapping of the spherical s-orbitals provides an efficient transport path.[41] The electron transport in the amorphous n-type IZO channel layer is dominated by electron hopping between neighboring cation ions (Figure 7a). Before participating in the conducting transport, the induced electrons have to fill the localized states between the energy gaps (Figure 7b). In the TFTs with an identical device structure, the amount of charge carriers induced by the external electric field are proportional to the capacitance of the gate insulator. Therefore, when the high-k ScO $_r$  films were used as the gate dielectric, a large amount of attracted electrons quickly filled the lower-lying localized states in the oxide semiconductors. Then, the additionally accumulated electrons could occupy the upper-lying localized states. As a result, the electrons could jump to the neighboring localized states easily, along the percolating-conduction path, which resulted in an enhanced electron mobility.

## 2.7. Solution-Processed p-Type CuO/ScO<sub>x</sub> TFTs

After the successful fabrication of high-performance n-type IZO TFTs based on high- $k~{\rm ScO}_x$  dielectric, we also attempted to demonstrate the feasibility of solution-processed p-type TFTs based on the  ${\rm ScO}_x$  dielectric layer. As previously mentioned, previously reported solution-processed p-type oxide TFTs exhibited low electrical performances, which significantly limited the development of fully-oxide low-power consumption CMOS logics. In order to prepare high-quality p-type oxide films, the most straightforward way is to control the oxidation of the metallic layer. [26,42] In this work a polyol reduction method was adopted to synthesize the metallic layer because of its low-temperature process possibilities and electrical characteristics. [43]

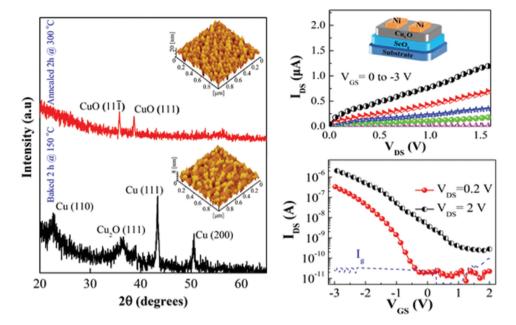

Figure 8. a) XRD patterns of the CuO thin film annealed at 150 °C and 300 °C in air for 2 h. The insets show the AFM images of the corresponding films. b) Output and c) transfer characteristics of the CuO/ScO<sub>x</sub> TFT under different  $V_{DS}$ . Here, the dotted line corresponds to the off current ( $I_{off}$ )

Polyalcohols, such as ethylene glycol and glycerol, hereby act as the solvent as well as the mild reducing agent.

In this work copper oxide (CuO), known to be a typical p-type oxide material, was used as the TFT channel layer and was incorporated in TFTs with a  $ScO_x$  dielectric. As shown in **Figure 8**a, the CuO gel was decomposed into metallic copper at a low temperature of 150 °C. The 300 °C-annealed CuO film, used as the TFT channel, consisted of a mixture of CuO (11 $\overline{1}$ ) and CuO (111). The surface morphologies revealed that the CuO film that was annealed at 300 °C had a uniform surface (RMS = 3.9 nm) with an average grain size of 40 nm. It is well known that the electrical performance of the TFTs strongly depends on the surface roughness and the crystalline structure of the thin films. [25] Thus, films with smooth surfaces and large grain sizes lead to less grain boundaries, which is beneficial to improve the hole mobility and the reliability of the TFTs.

The output and transfer characteristics of the p-type CuO/ScO $_x$  TFTs are shown in Figure 8b,c. CuO TFTs based on a SiO $_2$  dielectric were also fabricated for comparison. The key electrical parameters of the TFT devices are summarized in **Table 1**. Note that the  $I_{\rm DS}$  monotonically increases as the gate voltage  $V_{\rm GS}$  is reduced from 0 to -3 V, which is a typical characteristic of

Table 1. Electrical parameters of the n-type IZO and p-type CuO TFT based on  ${\rm SiO_2}$  and  ${\rm ScO_x}$  dielectrics. <sup>a)</sup>

| TFT structure        | $\mu_{\rm FE}$ [cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> ] | $I_{\rm on}/I_{\rm off}$ | V <sub>TH</sub><br>[V]            | SS<br>[V dec <sup>-1</sup> ] |

|----------------------|-------------------------------------------------------------------|--------------------------|-----------------------------------|------------------------------|

| IZO/SiO <sub>2</sub> | $3.35\pm0.25$                                                     | ~108                     | $1.50 \pm 0.20$                   | $0.5\pm0.02$                 |

| $IZO/ScO_x$          | 27.71 ± 1.15                                                      | ~10 <sup>7</sup>         | $\textbf{0.52} \pm \textbf{0.04}$ | ~0.1                         |

| CuO/SiO <sub>2</sub> | $\textbf{0.26} \pm \textbf{0.04}$                                 | $10^5 - 10^6$            | $-8.2\pm0.50$                     | $1.9 \pm 0.10$               |

| CuO/ScO <sub>x</sub> | $0.78 \pm 0.03$                                                   | ~105                     | $-0.6 \pm 0.05$                   | ~0.4                         |

$<sup>^{</sup>a)}$ Each device metric is the average of 12 devices (3  $\times$  4 array).

a TFT with a p-type channel. The non-ideal current saturation behavior in the output curves can be due to two main reasons. The first one is related to a poor CuO film quality, which can be caused by the agglomeration of the CuO nanopowders.<sup>[5b]</sup> The second reason is related to the relatively high hole concentration in the CuO channel layer.<sup>[44]</sup> Overall, the p-type device exhibits promising operating characteristics with large  $I_{\rm on}/I_{\rm off}$  values ( $\sim 10^5$ ) and a hole mobility of around 0.8 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. The hole mobility achieved in this report is much larger than previously reported values regarding solution-processed Cu-based oxides as channel layers (in the range of 0.001 to 0.22 cm $^2$  V $^{-1}$  s $^{-1}$ ). $^{[25-28]}$ The improved features are undoubtedly related to the highk ScO<sub>x</sub> dielectric, high-quality CuO channel layer, and the electronically clean interface of CuO/ScOx, which can be concluded by comparing these results to the ones achieved using a CuO/SiO<sub>2</sub> system, as shown in Table 1.

In recent reports of solution-processed TFTs, high-mobilitydriven studies that were carried out suffered from small  $I_{\rm on}/I_{\rm off}$  and large  $I_{\rm off}$  values (>10<sup>-9</sup> A). [10a,40,45] The large  $I_{\rm off}$ value undoubtedly results in more power dissipation, and yields unstable and unreliable TFTs. In those reports, the highk dielectrics were prepared using organic-based precursor solutions. During the post-annealing process, the pyrolysis of organic ligands tends to release a large amount of volatile gases, which would generate nanopores in the resultant dielectric films. This in turn is problematic for high-performance electronic devices. However, in this report, the organicfree WI precursor solution can effectively reduce the formation of volatile gases. In addition, the UV-assisted pre-treatment allows the moderation of the decomposition of the NO<sub>3</sub><sup>-</sup> species in the gel film, which makes the surface roughness and surface energy small.<sup>[46]</sup> As a result, the TFTs based on highquality  $ScO_x$  dielectrics exhibit high  $I_{on}/I_{off}$  values with a low  $I_{\rm off}$  of around  $10^{-11}$  A.

\_\_\_ MATERIALS

www.afm-iournal.de

www.MaterialsViews.com

#### 3. Conclusions

Novel ScO<sub>x</sub> dielectric thin films were fabricated via a waterinducement route for the first time. Here, the precursor solution for the preparation of the ScO<sub>x</sub> thin films contained water and metal nitrates without additional organic additives and catalysts. The physical properties of the WI ScOx films were characterized using different structural, morphological, composition, optical, and electrical techniques. The results showed that ScOx thin films annealed at 250-550 °C exhibit a high transparency (>90%), smooth surface (<0.6 nm), and are amorphous. To verify the possible application of the ScO<sub>x</sub> thin films as the gate dielectric in low-temperature-processed (≤350 °C) CMOS logics, n-type IZO and p-type CuO channelbased TFTs were integrated on the prepared ScO<sub>x</sub> dielectric thin films. Both n- and p-type TFTs exhibited improved electrical performances at much lower operating voltages compared to those of SiO<sub>2</sub>-based TFTs. In particular, the p-type CuO/ScO<sub>4</sub> TFT exhibited a much higher electrical performance under a gate bias of 3 V, with an  $I_{\rm on}/I_{\rm off}$  value of around 10<sup>5</sup> and hole mobility of 0.8 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. To the best of our knowledge, this is the first report on such high performances for solution-processed p-type oxide TFTs based on a high-k dielectric, which represents a great step towards the development of next-generation, low-cost, all-oxide CMOS electronics.

## 4. Experimental Section

Precursor Solution Preparation and Characterization: The WI  $ScO_x$  precursor solution (0.1 M) was prepared by dissolving  $Sc(NO_3)_3 \cdot 6H_2O$  in deionized (DI) water. The 0.1 M IZO precursor solution was prepared by dissolving  $In(NO_3)_3 \cdot H_2O$  and  $Zn(NO_3)_2 \cdot H_2O$  in DI water. The molar ratio of In/Zn was 7:3. The CuO precursor solution with a concentration of 0.1 M was prepared by dissolving  $Cu(NO_3)_2 \cdot 3H_2O$  in a mixture of DI water and glycerol. The method was reported somewhere else. [28] After that, these precursor solutions were stirred for 6 h before fabrication. The thermal behavior of the  $ScO_x$  xerogel was monitored under ambient air using a thermogravimetric analyzer (TGA, Pyris 1) at a heating rate of  $10 \, ^{\circ}C$  min $^{-1}$ .

Thin Film Fabrication and Characterization: Prior to thin-film fabrication, heavily doped p-type Si substrates were cleaned ultrasonically in acetone, ethanol, and then DI water and dried by N2 gun. The ScOx solution was filtered through a 0.22-µm polytetrafluoroethylene (PTFE) syringe filter and then spun on the hydrophilic Si substrates at 500 rpm for 5 s and 5000 rpm for 20 s. Before the thermal annealing process was carried out, the ScO<sub>x</sub> samples were treated by UV-assisted irradiation for 30 min. For convenience, the ScO<sub>x</sub> thin films annealed at 250, 350, 450, and 550 °C, hereafter, will be abbreviated as ScO<sub>x</sub>-250, ScO<sub>x</sub>-350, ScO<sub>x</sub>-450, and ScO<sub>x</sub>-550, respectively. The thicknesses of ScO<sub>x</sub>-250, ScO<sub>x</sub>-350, ScO<sub>x</sub>-450, and ScO<sub>x</sub>-550, measured by spectroscopic ellipsometry (ESS01, Sofn Instrument), were 28, 23, 23, and 25 nm, respectively. The transmittances of ScO<sub>x</sub> films on sapphire were analyzed by UV-vis spectroscopy (UV-2550, Shimadzu). The crystal structures of ScO<sub>x</sub> and Cu<sub>x</sub>O thin films were investigated by X-ray diffractometry (XRD, X'Pert-PRO, PANalytical, Holland) with  $CuK\alpha 1$  radiation. The surface morphologies of  $ScO_x$  and  $Cu_xO$  films were measured by using an atomic force microscope (AFM, SPA-400, Seiko). The chemical compositions of the ScO<sub>x</sub> films were analyzed by X-ray photoelectron spectroscopy (XPS, ESCALAB 250).

Electronic Device Fabrication and Characteristics: To fabricate the WI n-type IZO TFTs based on the  $ScO_x$  dielectric, the IZO precursor was spin-coated on the  $ScO_x$ -350 dielectric at 5000 rpm for 25 s. The laminated samples were subsequently annealed at 300 °C for 120 min. After that, the AI source and drain electrodes were evaporated on the IZO channel

layer through a shadow mask. To fabricate the p-type CuO TFTs based on the ScO<sub>v</sub> dielectric layer, the CuO precursor solution was spin-coated on the ScO<sub>2</sub>-350 dielectric at 5000 rpm for 25 s. The laminated samples were subsequently annealed at 300 °C for 120 min. The Ni source and drain electrodes were then evaporated on CuO channel layer through a shadow mask. In this report, the channel length and width of the TFTs were 250 and 1000 µm, respectively. For comparison, the n-type IZO and p-type CuO TFTs based on a thermally grown SiO<sub>2</sub> (100 nm) dielectric layer were also fabricated, which were used as reference devices. To examine the dielectric properties of the ScO<sub>x</sub> thin films, capacitors with a structure of Al/ScO<sub>x</sub>/p<sup>+</sup>-Si were fabricated and investigated using an impedance analyzer (4294A, Agilent). The electrical properties of the ScO<sub>v</sub> capacitors and the integrated TFT devices were measured under ambient conditions using a semiconductor parameter analyzer (Keithley 2634B) in a dark box. The field-effect mobility ( $\mu_{FE}$ ) was extracted from the transfer characteristics using:[1]

$$I_{DS} = \left(\frac{W}{2L}C_i\mu_{FE}\right)\left(V_{G} - V_{TH}\right)^2 \tag{1}$$

where  $C_i$  is the areal capacitance of the dielectric; W and L are the channel width and length of the TFT, respectively;  $V_G$  is the gate voltage and  $V_{TH}$  is the threshold voltage, which can be determined in the saturation region by the linear fitting of the  $I_D^{1/2}$  vs.  $V_G$  plot. The maximum areal density of states ( $N_s^{max}$ ) of the TFT device was calculated using:[47]

$$SS = \frac{\kappa T \ln 10}{e} \left[ 1 + \frac{e^2}{c_i} N_s^{\text{max}} \right]$$

(2)

where k is the Boltzmann constant, e is the electron charge, SS is the subthreshold swing of the transfer curve.

#### **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

## Acknowledgements

This work was supported by the Natural Science Foundation of China (Grant nos. 51472130 and 51572135).

Received: June 26, 2015 Revised: August 30, 2015 Published online: October 21, 2015

a) E. Fortunato, P. Barquinha, R. Martins, Adv. Mater. 2012, 24, 2945; b) T. Kamiya, K. Nomura, H. Hosono, Sci. Technol. Adv. Mater. 2010, 11, 044305; c) T. Chang, C. Chiu, W. Weng, S. Chang, T. Tsai, Z. Huang, Appl. Phys. Lett. 2012, 101, 261112; d) X. Chen, P. Lin, X. Yan, Z. Bai, H. Yuan, Y. Shen, Y. Liu, G. Zhang, Z. Zhang, Y. Zhang, ACS Appl. Mater. Interfaces 2015, 7, 3216; e) J. Jung, S. J. Kim, K. W. Lee, D. H. Yoon, Y. G. Kim, H. Y. Kwak, S. R. Dugasani, S. H. Park, H. J. Kim, Biosens. Bioelectron. 2014, 55, 99.

<sup>[2]</sup> a) Y. M. Park, J. Daniel, M. Heeney, A. Salleo, Adv. Mater. 2011, 23, 971; b) M. Esro, R. Mazzocco, G. Vourlias, O. Kolosov, A. Krier, W. I. Milne, G. Adamopoulos, Appl. Phys. Lett. 2012, 106, 203507; c) D. Afouxenidis, R. Mazzocco, G. Vourlias, P. J. Livesley, A. Krier, W. I. Milne, O. Kolosov, G. Adamopoulos, ACS Appl. Mater. Interfaces 2015, 7, 7334; d) S. T. Meyers, J. T. Anderson, D. Hong, C. M. Hung, J. F. Wager, D. A. Keszler, Chem. Mater. 2007, 19, 4023.

www.afm-iournal.de

www.MaterialsViews.com

- [3] a) W. Xu, H. Wang, L. Ye, J. Xu, J. Mater. Chem. C 2014, 2, 5389; b) J. Robertson, R. M. Wallace, Mater. Sci. Eng. R 2015, 88, 1.

- [4] a) H. Klauk, U. Zschieschang, J. Pflaum, M. Halik, Nature 2007, 445, 745; b) D. O. Hutchins, T. Weidner, J. Baio, B. Polishak, O. Acton, N. Cernetic, H. Ma, A. K. Y. Jen, J. Mater. Chem. C 2013, 1, 101.

- [5] a) H. Liu, J. Sun, Q. Tang, Q. Wan, J. Phys. Chem. C 2010, 114, 12316; b) T. T. Baby, S. K. Garlapati, S. Dehm, M. H. Ming, R. Kruk, H. Hahn, S. Dasgupta, ACS Nano 2015, 9, 3075.

- [6] H. Xu, D. Luo, M. Li, M. Xu, J. Zou, H. Tao, L. Lan, L. Wang, J. Peng, Y. Cao, J. Mater. Chem. C 2014, 2, 1255.

- [7] a) H. Zhang, L. Liang, A. Chen, Z. Liu, Z. Yu, H. Cao, Q. Wan, Appl. Phys. Lett. 2010, 97, 122108; b) L. Zhang, J. Li, X. Zhang, X. Jiang, Z. Zhang, Appl. Phys. Lett. 2009, 95, 072112.

- [8] a) M. Esro, G. Vourlias, C. Somerton, W. I. Milne, G. Adamopoulos, Adv. Funct. Mater. 2015, 25, 134; b) P. N. Plassmeyer, K. Archila, J. F. Wager, C. J. Page, ACS Appl. Mater. Interfaces 2015, 7, 1678.

- [9] K. Song, W. Yang, Y. Jung, S. Jeong, J. Moon, J. Mater. Chem. 2012, 22, 21265.

- [10] a) P. K. Nayak, M. Hedhili, D. Cha, H. Alshareef, Appl. Phys. Lett. 2013, 103, 033518; b) G. Adamopoulos, S. Thomas, D. D. Bradley, M. A. McLachlan, T. D. Anthopoulos, Appl. Phys. Lett. 2011, 98,

- [11] G. X. Liu, A. Liu, F. K. Shan, Y. Meng, B. C. Shin, E. Fortunato, R. Martins, Appl. Phys. Lett. 2014, 105, 113509.

- [12] X. Zou, G. Fang, L. Yuan, M. Li, W. Guan, X. Zhao, IEEE Electron Device Lett. 2010, 31, 827.

- [13] a) G. D. Wilka, R. M. Wallace, Appl. Phys. Lett. 1999, 74, 2854; b) G. D. Wilka, R. M. Wallace, Appl. Phys. Lett. 2000, 76, 112.

- [14] a) X. Wang, O. I. Saadat, B. Xi, X. Lou, R. J. Molnar, T. Palacios, R. G. Gordon, Appl. Phys. Lett. 2012, 101, 232109; b) J. J. Chen, B. Gila, M. Hlad, A. Gerger, F. Ren, C. Abernathy, S. Pearton, Appl. Phys. Lett. 2006, 88, 142115; c) P. Feijoo, A. D. Prado, M. Toledano-Luque, E. S. Andrés, M. Lucía, J. Appl. Phys. 2010, 107, 084505.

- [15] J. F. Wager, D. A. Keszler, R. E. Presley, Transparent Electronics, Springer, New York, NJ 2008, p. 80.

- [16] S. Wolf, Silicon Processing for the VLSI Era, Vol. 4, Lattice, Sunset Beach, CA, USA 2002.

- [17] Y. Zhao, K. Kita, A. Toriumi, Appl. Phys. Lett. 2010, 96, 242901.

- [18] R. F. P. Martins, A. Ahnood, N. Correia, L. M. N. P. Pereira, R. Barros, P. M. C. B. Barquinha, R. Costa, I. M. M. Ferreira, A. Nathan, E. E. M. C. Fortunato, Adv. Funct. Mater. 2013, 23, 2153.

- [19] A. P. Milanov, K. Xu, S. Cwik, H. Parala, T. de los Arcos, H. W. Becker, D. Rogalla, R. Cross, S. Paul, A. Devi, Dalton Trans. **2012**, 41, 13936.

- [20] G. Liu, Y. Jin, H. He, Z. Fan, Thin Solid Films 2010, 518, 2920.

- [21] Y. S. Rim, W. H. Jeong, D. L. Kim, H. S. Lim, K. M. Kim, H. J. Kim, J. Mater. Chem. 2012, 22, 12491.

- [22] K. Jiang, S. T. Meyers, M. D. Anderson, D. C. Johnson, D. A. Keszler, Chem. Mater. 2013, 25, 210.

- [23] a) A. Liu, G. X. Liu, H. H. Zhu, F. Xu, E. Fortunato, R. Martins, F. K. Shan, ACS Appl. Mater. Interfaces 2014, 6, 17364; b) G. X. Liu, A. Liu, H. H. Zhu, B. C. Shin, E. Fortunato, R. Martins, Y. Q. Wang, F. K. Shan, Adv. Funct. Mater. 2015, 25, 2564.

- [24] E. Fortunato, R. Barros, P. Barquinha, V. Figueiredo, S. K. Park, C. S. Hwang, R. Martins, Appl. Phys. Lett. 2013, 102, 163505.

- [25] S. Y. Kim, C. H. Ahn, J. H. Lee, Y. H. Kwon, S. Hwang, J. Y. Lee, H. K. Cho, ACS Appl. Mater. Interfaces 2010, 97, 052105.

- [26] P. Pattanasattayavong, S. Thomas, G. Adamopoulos, M. A. McLachlan, T. D. Anthopoulos, Appl. Phys. Lett. 2013, 102, 163505.

- [27] K. Okamura, B. Nasr, R. A. Brand, H. Hahn, J. Mater. Chem. 2012, 22, 4607.

- [28] S. K. Garlapati, T. T. Baby, S. Dehm, M. Hammad, V. S. K. Chakravadhanula, R. Kruk, H. Hahn, S. Dasgupta, Small 2015, 11, 3591.

- [29] K. W. Jo, W. J. Cho, Phys. Status Solidi A 2014, 211, 2817.

- [30] K. Choi, M. Kim, S. Chang, T. Y. Oh, S. W. Jeong, H. J. Ha, B. K. Ju, Jpn. J. Appl. Phys. 2013, 52, 060204.

- [31] a) D. Yoo, I. Kim, S. Kim, C. H. Hahn, C. Lee, S. Cho, Appl. Surf. Sci. 2007, 253, 3888; b) V. Gupta, A. Mansingh, J. Appl. Phys. 1996, 80, 1063.

- [32] X. G. Yu, L. Zeng, N. Zhou, P. Guo, F. Shi, D. B. Buchholz, Q. Ma, J. Yu, V. P. Dravid, R. P. H. Chang, M. Bedzyk, T. J. Marks, A. Facchetti, Adv. Mater. 2015, 27, 2390.

- [33] M. Liu, Q. Fang, G. He, L. Li, L. Zhu, G. Li, L. Zhang, Appl. Phys. Lett. 2006, 88, 192904.

- [34] C. G. Lee, A. Dodabalapur, J. Electron. Mater. 2012, 41, 895.

- [35] W. F. Chung, T. C. Chang, H. W. Li, S. C. Chen, Y. C. Chen, T. Y. Tseng, Y. H. Tai, Appl. Phys. Lett. 2011, 98, 152109.

- [36] J. H. Park, Y. B. Yoo, K. H. Lee, W. S. Jang, J. Y. Oh, S. S. Chae, H. K. Baik, ACS Appl. Mater. Interfaces 2013, 5, 410.

- [37] S. M. Hwang, S. M. Lee, K. Park, M. S. Lee, J. Joo, J. H. Lim, H. Kim, J. J. Yoon, Y. D. Kim, Appl. Phys. Lett. 2011, 98, 022903.

- [38] K. M. Kim, C. W. Kim, J. S. Heo, H. Na, J. E. Lee, C. B. Park, J. U. Bae, C. D. Kim, M. Jun, Y. K. Hwang, Appl. Phys. Lett. 2011, 99, 242109.

- [39] Y. G. Kim, C. Avis, J. Jang, ECS Solid State Lett. 2012, 1, Q23.

- [40] W. Y. Xu, H. Wang, F. Xie, J. Chen, H. Cao, J. B. Xu, ACS Appl. Mater. Interfaces 2015, 7, 5803.

- [41] E. Lee, J. Ko, K. H. Lim, K. Kim, S. Y. Park, J. M. Myoung, Y. S. Kim, Adv. Funct. Mater. 2014, 24, 4689.

- [42] a) J. Jiang, X. Wang, Q. Zhang, J. Li, X. Zhang, Phys. Chem. Chem. Phys. 2013, 15, 6875; b) H. N. Lee, B. J. Song, J. C. Park, J. Display Technol. 2014, 10, 288.

- [43] K. J. Carroll, J. U. Reveles, M. D. Shultz, S. N. Khanna, E. E. Carpenter, J. Phys. Chem. C 2011, 115, 2656.

- [44] H. A. Al-Jawhari, J. A. Caraveo-Frescas, M. Hedhili, H. N. Alshareef, ACS Appl. Mater. Interfaces 2013, 5, 9615.

- [45] a) M. G. Kim, M. G. Kanatzidis, A. Facchetti, T. J. Marks, Nat. Mater. 2011, 10, 382; b) E. J. Bae, Y. H. Kang, M. Han, C. Lee, S. Y. Cho, J. Mater. Chem. C 2014, 2, 5695; c) W. Yang, K. Song, Y. Jung, S. Jeong, J. Moon, J. Mater. Chem. C 2013, 1, 4275; d) G. Adamopoulos, S. Thomas, P. H. Wöbkenberg, D. D. C. Bradley, M. A. McLachlan, T. D. Anthopoulos, Adv. Mater. 2011, 23, 1894.

- [46] J. Hwang, K. Lee, Y. Jeong, Y. U. Lee, C. Pearson, M. C. Petty, H. Kim, Adv. Mater. Interfaces 2014, 1, 1400206.

- [47] W. L. Kalb, B. Batlogg, Phys. Rev. B 2010, 81, 035327.